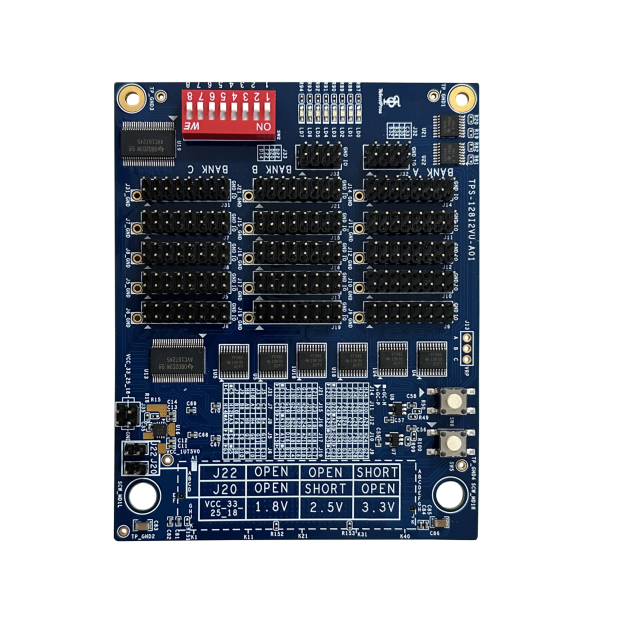

IO Translator Board

High-Precision Level Shifting for Diverse Interface Prototyping.

靈活解決 FPGA 與外設間的電壓不匹配問題,保障系統間的高速數據通訊品質。

Versatile Level Shifting

支援寬電壓準位轉換,確保不同 I/O Bank 規範間的電壓完美對接。

Fast-to-Market

成熟的轉換電路方案,省去工程師自行研發 Level Shifter 的時間成本。

Signal Integrity

優化的訊號路徑設計,最小化轉換過程中的延遲與抖動,維持數據品質。

跨越電壓藩籬,實現穩定的系統橋接

在複雜的 SoC 驗證場景中,FPGA 主板與測試周邊往往操作在不同的電壓環境。聯豪科創 **IO Translator Board** 專為解決此類介面相容性難題而設計,為您的驗證體系提供堅實的保護與高效的通訊。

- 高速訊號整合 (High-speed signal integrity): 針對高速數位訊號進行優化,確保在準位轉換後依然能維持清晰的眼圖表現。

- 縮短上市時程 (Time-to-market): 提供模組化設計,讓團隊能夠在數小時內完成介面跳接與驗證環境搭建。

- 保護精密元件: 內建隔離保護機制,有效防止因電壓不匹配導致的 FPGA 針腳損壞風險。

- 高彈性接口配置: 相容多種子板規格,支援從低速控制訊號到高速數據介面的全方位轉換。

Technical Specifications

| IO Translator Board Specifications | |

|---|---|

| Level Shifting Range | Wide Range (e.g., 1.2V to 3.3V Support) |

| I/O Channels | Multi-channel High-density Signal Routing |

| Board Interface | Standard TalentPros Daughter Card Connector |

| Signal Delay | Ultra-low Latency Conversion |

| Compatibility | TalentPros VU19P, VU13P, VU9P & KU Series |

| Protection Features | Over-voltage / ESD Protection Ready |

Request Full Specifications

Detailed datasheets and technical documentation are available upon request.

Please contact our team for more information regarding the IO Translator Board