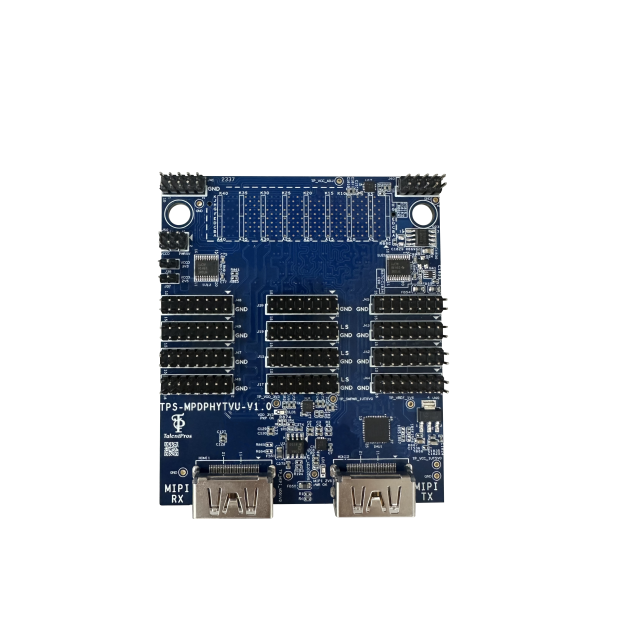

MIPI D-PHY Board

Advanced High-Speed Video Interface for Camera and Display Prototyping.

解鎖行動影像驗證能力,為 SoC 的 CSI-2/DSI 影像 IP 提供最穩定且精準的物理層支撐。

Mobile & Auto Vision

針對行動通訊與車載鏡頭驗證設計,支援高速影像數據流的精準採集與輸出。

Fast-to-Market

預先優化的 D-PHY 硬體佈局,免去研發團隊自行調校高速差分訊號的負擔,加速上市時程。

Signal Integrity

極致的高速訊號整合能力,確保在 HS (高速) 與 LP (低功耗) 模式切換下的波形穩定與正確性。

定義高效能影像驗證的技術基石

在 SoC 影像 IP 開發中,MIPI D-PHY 的物理層驗證是最具技術門檻的環節之一。聯豪科創 **MIPI D-PHY Board** 專為解決高頻訊號衰減、時鐘歪斜(Clock Skew)與複雜的模式切換問題而生,為您的影像開發提供最強大的硬體後盾。

- 高速訊號整合 (High-speed signal integrity): 採用低損耗 PCB 材料與精密差分阻抗控制,確保單通道在極速運行下依然維持開闊的眼圖表現。

- 縮短上市時程 (Time-to-market): 提供即插即用的 MIPI 介面方案,讓研發團隊能第一時間進入 CSI-2/DSI 協定層驗證與算法調校。

- 支援多元應用: 完美銜接多種規格的鏡頭模組與顯示面板,支援從單通道到多通道(Multi-lane)的靈活配置。

- 精密電路保護: 內建專用電平轉換與 ESD 保護設計,嚴密守護 FPGA 主板 I/O 安全,防止驗證過程中的意外損傷。

Technical Specifications

| MIPI D-PHY Board Specifications | |

|---|---|

| MIPI Standard | Compliant with MIPI D-PHY Specification (v1.2/v2.1 Ready) |

| Lane Configuration | 1 Clock Lane + 4 Data Lanes Support |

| Operation Modes | High-Speed (HS) & Low-Power (LP) Mode Supported |

| Protocol Pairing | Compatible with MIPI CSI-2 & DSI Controller IPs |

| Signal Integrity | Optimized Trace Length Matching for All Lanes |

| Compatibility | TalentPros VU19P, VU13P, VU9P & VP Series |

Request Full Specifications

Detailed datasheets and technical documentation are available upon request.

Please contact our team for more information regarding the MIPI D-PHY Board