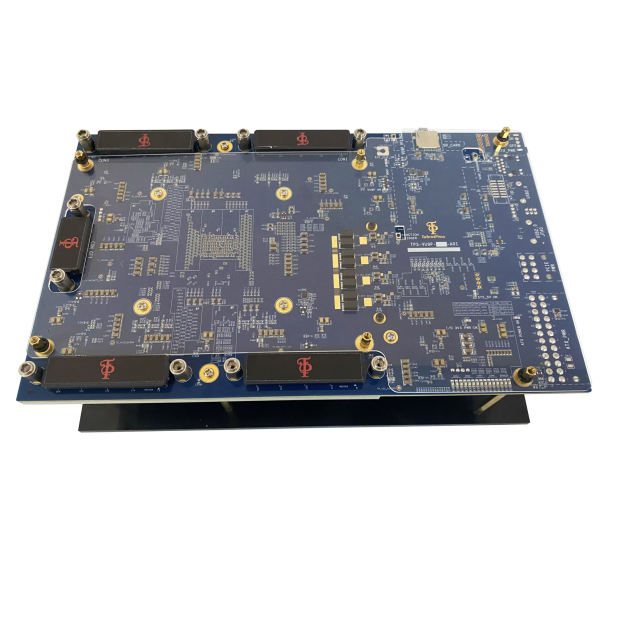

TPS-VU9P IEP

Empowering Large-Scale SoC Innovation with Scalable Capacity and Intelligent Control.

工業級輕量化機構、智慧監控、遠端部署:TPS m-View 讓硬體驗證更簡單、更可靠。

Lite & Flexible

輕量化設計降低硬體部署門檻,專為工業環境 PoC 驗證與現場展示設計。

Industrial Connectivity

具備 627 組 HP IO,提供豐富的數據介面,優化工業級系統整合表現。

Smart Reliability

整合 TPS m-View 智慧管理中心,支援自我診斷與即時功耗監控,確保流程萬無一失。

精準驗證,縮短工業 SoC 開發週期

TPS-VU9P IEP 搭載 Xilinx Virtex UltraScale+ 核心,結合 16nm 先進製程與優異的高速訊號整合 (High-speed signal integrity) 能力,是追求開發效率與硬體穩定性的首選平台。透過智慧保護機制,我們協助客戶在確保硬體安全的同時,大幅優化產品的上市時程 (Time-to-market)。

- 高性能邏輯資源: 具備 3,780K 系統邏輯單元與 454.5Mb 內部記憶體。

- PoC 展示利器: 輕量化 Lite 機構設計,大幅提升現場部署與演示的便利性。

- 智慧型管理中心: 支援遠端燒錄、Self-Test 自我診斷及即時溫度偵測。

- 彈性擴充架構: 支援多規格 Daughter Cards,無縫對接多樣化的工業通訊接口。

Standard Configuration

內建標準通訊接口,優化數據存取與 Debug 流程:

USB 2.0 / Gigabit Ethernet / JTag / Micro SD Card

Security Protection

軍規級 AES-Key 256-bit 加密技術,嚴密保護您的核心設計 IP:

AES-Key 256-bit Encryption Support

Technical Specifications

| TPS-VU9P IEP Hardware Resources | |

|---|---|

| Process Technology | 16nm Virtex UltraScale+ Architecture |

| System Logic Cell | 3,780 K |

| VCCINT Core Power | 150A |

| Internal Memory | 454.5 Mb (Block RAM: 94.5Mb, Ultra RAM: 360Mb) |

| Transceivers Max Rate | GTY: 16 Gbps |

| HP IO Count | 627 |

| GTY Transceivers | 16 (TX/RX) |

| PCIe Compatibility | Gen4 / Gen3 Supported |

| MIPI D-PHY | 1.5 Gbps |

Request Full Specifications

Detailed datasheets and technical documentation are available upon request.

Please contact our team for more information regarding the TPS-VU9P-IEP