TPSIC FPGA Rapid2 Partition

Automating Multi-FPGA Design Partitioning for Next-Gen SoC Prototyping.

突破單片 FPGA 容量限制,以智慧化自動切割軟體加速大規模設計的部署與驗證。

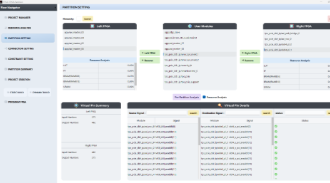

自動跨平台訊號偵測

精準掃描 RTL 代碼,智慧識別並導出所有需要跨越 FPGA 邊界的關鍵訊號,建立清晰的互聯藍圖。

訊號分類與異常預警

自動分類訊號屬性,即時識別位元寬度衝突、懸空連線等異常,在合成前排除 90% 的潛在整合問題。

結構化 IP Mapping

支援 TDM (時分多工)、DIO 與 AXI 匯流排定義,自動化建立高效的高速跨片對接點 (Bridge Nodes)。

自動 RTL Wrapper 產生

一鍵生成各片 FPGA 的 Top-Level 封裝、Bridge IP 實例及其連線關係,大幅取代人工編寫的工作量。

Vivado 流程無縫整合

產出格式直接對應 Vivado 專案結構,確保軟體切割後的結果能直接導入現有的 EDA 工作流。

增量重新合成支援

具備局部更新能力,當設計微調時,FPGA 不需要重新合成整個設計,顯著提升開發迭代效率。

跨越規模限制,釋放多片 FPGA 驗證潛能

大規模 SoC 驗證最艱鉅的挑戰在於如何將複雜的 Netlist 切割至多片 FPGA 而不喪失效能。**TPSIC FPGA Rapid2 Partition** 透過自動化演算法,將原本耗時數週的手動切割縮短至數小時。

- 高速訊號整合 (High-speed signal integrity): 自動優化 TDM 插入點,確保跨片通訊的時序收斂與訊號完整性。

- 縮短上市時程 (Time-to-market): 自動化封裝與專案生成功能,讓團隊能將精力集中於 Bug 除錯而非繁瑣的環境搭建。

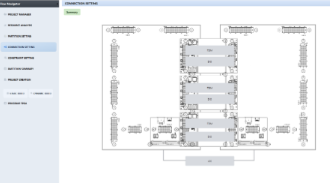

- 視覺化管理: 整合圖形介面,讓工程師能直觀地管理訊號分配與互聯關係。

- 極致的流程相容性: 支援主流 FPGA 供應商流程,是聯豪科創 VU19P 及 VP1902 多片系統的軟體靈魂。

Request Full Specifications

Detailed software documentation and evaluation licenses are available upon request.

Please contact our team for more information regarding TPSIC FPGA Rapid2 Partition