全部產品服務

-

MORE

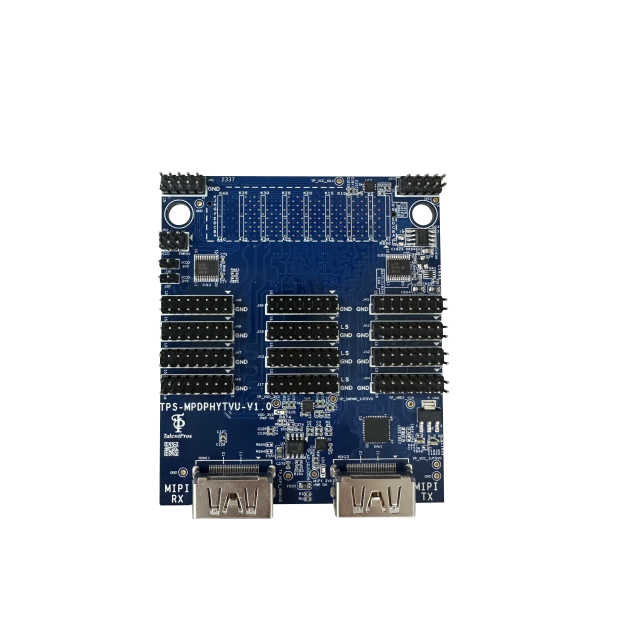

MIPI D-PHY Board

MIPI D-PHY BoardMIPI D-PHY Board

MIPI D-PHY Board

MIPI TX PORT *1 (MIPI PHY CHIP MC20902)

MIPI RX PORT *1 (MIPI PHY CHIP MC20901)

Reserve IO *79 (Directly connected to FPGA) Reserve IO *24 (Connected to FPGA through Level Shifter, can be set to 1.8V, 2.5V, 3.3V) Total Reserve IO *103

Reserve 5V Power: 2 Pin Header -

MORE

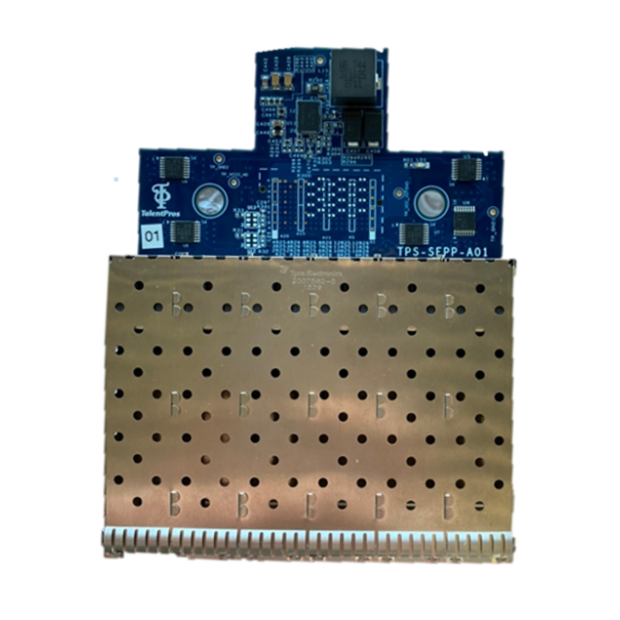

Loopback Card

Loopback CardLoopback Card

Loopback Card

Self-diagnostic program includes:

.System BOOT detection

.Voltage detection

.I/O detection

.GTY I/O testing

.HP I/O testing

.DDR4 SODIMM testing -

MORE

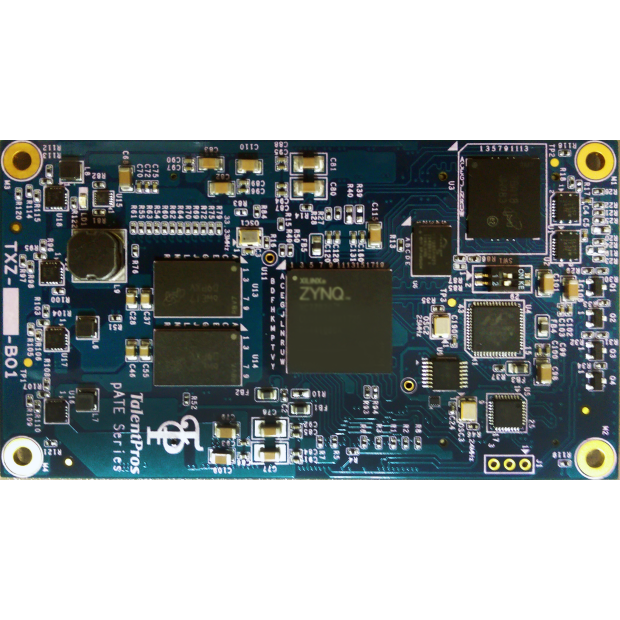

FPGA ARM based SOC module : TXZ-1300

FPGA ARM based SOC module : TXZ-1300FPGA ARM based SOC module : TXZ-1300

/* 聯豪科創 統一產品頁面設計規範 */

.tp-product-page { color: #333; font-family: "Segoe UI", "Roboto", "PingFang TC", sans-serif; line-height: 1.7; }

.tp-main-color { color: #0d1735; }

.tp-section { padding: 60px 20px; max-width: 1200px; margin: 0 auto; }

/* Hero Header - 深藍科技漸層 */

.tp-product-hero { background: linear-gradient(135deg, #0d1735 0%, #000 100%); color: #fff; padding: 80px 20px; text-align: center; border-radius: 0 0 50px 50px; }

.tp-product-hero h1 { font-size: 42px; margin-bottom: 15px; font-weight: 800; letter-spacing: 1px; }

.tp-product-hero p { font-size: 18px; opacity: 0.9; max-width: 800px; margin: 0 auto; font-style: italic; }

/* Feature Grid - 俐落三欄式佈局 */

.tp-feature-grid {

display: grid;

grid-template-columns: repeat(3, 1fr);

gap: 30px;

margin: 40px 0;

}

.tp-feature-item { text-align: center; padding: 30px 20px; background: #fdfdfd; border: 1px solid #eee; border-radius: 12px; transition: 0.3s; height: 100%; box-sizing: border-box; }

.tp-feature-item:hover { box-shadow: 0 10px 30px rgba(0,0,0,0.08); transform: translateY(-5px); }

.tp-feature-item i { font-size: 40px; color: #0d1735; margin-bottom: 15px; display: block; }

.tp-feature-item h3 { font-size: 18px; color: #0d1735; margin-bottom: 12px; font-weight: 700; }

/* Tech Highlights Section */

.tp-highlight-content { background: #f4f7fa; padding: 40px; border-radius: 20px; margin-bottom: 50px; }

.tp-list { list-style: none; padding: 0; }

.tp-list li { position: relative; padding-left: 30px; margin-bottom: 15px; font-size: 16px; }

.tp-list li::before { content: "✔"; position: absolute; left: 0; color: #0d1735; font-weight: bold; }

/* Specification Table */

.tp-spec-container { overflow-x: auto; margin-top: 40px; }

.tp-spec-table { width: 100%; border-collapse: collapse; background: #fff; min-width: 600px; }

.tp-spec-table th { background: #0d1735; color: #fff; padding: 15px; text-align: left; font-size: 18px; }

.tp-spec-table td { padding: 12px 15px; border-bottom: 1px solid #eee; font-size: 15px; }

.tp-spec-table tr:nth-child(even) { background: #fafafa; }

.tp-spec-label { font-weight: 600; color: #0d1735; width: 30%; }

/* CTA Section */

.tp-cta-box { background: #0d1735; color: #fff; padding: 50px; text-align: center; border-radius: 20px; margin-top: 60px; }

.tp-cta-btn { display: inline-block; background: #fff; color: #0d1735 !important; padding: 15px 40px; border-radius: 50px; text-decoration: none; font-weight: 700; margin-top: 25px; transition: 0.3s; }

.tp-cta-btn:hover { background: #000; color: #fff !important; transform: scale(1.05); }

/* RWD */

@media (max-width: 992px) {

.tp-feature-grid { grid-template-columns: repeat(2, 1fr); }

}

@media (max-width: 600px) {

.tp-feature-grid { grid-template-columns: 1fr; }

.tp-product-hero h1 { font-size: 30px; }

}

TXZ-1300

Empowering Large-Scale SoC Innovation with Scalable Capacity and Intelligent Control.

融合 ARM 雙核實力與 FPGA 靈活邏輯,為嵌入式驗證提供高性能、高密度的異構運算核心。

All Programmable SoC

搭載 XC7Z020,無縫整合 ARM Cortex-A9 雙核心與可程式化邏輯,實現軟硬體協同優化。

Fast-to-Market

預先整合高容量 DDR3 與 GbE 通訊介面,省去繁瑣的主板開發,顯著縮短原型驗證上市時程。

High-Density I/O

多達 123 組可自定義 User I/O,支援 55 組 LVDS 差分對,提供極佳的系統擴展彈性。

定義嵌入式運算的靈活與強悍

TXZ-1300 是一款專為追求高整合度與低功耗設計的 SoC 模組。透過 Xilinx Zynq-7000 架構,它不僅能處理複雜的作業系統任務,還能同時執行硬體級的實時信號處理,是構建現代邊緣計算設備的核心首選。

高速訊號整合 (High-speed signal integrity): 透過精密佈線與阻抗控制,確保 1GB DDR3 與 GbE 在高速運行下的數據完整性。

縮短上市時程 (Time-to-market): 提供模組化設計與雙重板對板連接器(Board-to-board),讓團隊能快速開發自定義載板,降低部署風險。

完善的通訊資源: 內建 USB 2.0、GbE 與 USB-UART,滿足從基礎調試到大規模數據傳輸的多樣化通訊需求。

開發者友善設計: 具備 JTAG 偵錯口、用戶 LED 與按鈕,支援標準開發流程,大幅提升研發效率。

Technical Specifications

TXZ-1300 Hardware Resources

SoC Core

Xilinx Zynq-7000 (XC7Z020-1CLG400C)

Processor System (PS)

Dual-core ARM Cortex-A9

Internal Memory

1GB DDR3 SDRAM / 128Mb QSPI Flash

Communications

10/100/1000 Ethernet / USB 2.0 / USB-UART

User I/O Count

123 Total (115 PL, 8 PS MIO)

I/O Configuration

Up to 55 LVDS Pairs or 115 Single-ended I/O

Storage Expansion

Micro SD Card Interface Supported

Debug & Misc

JTAG Port / User LED / Push Button

Request Full Specifications

Detailed datasheets and technical documentation are available upon request.

Please contact our team for more information regarding the TXZ-1300

Request Datasheet Now -

MORE

FPGA ARM based SOC module : TXZ-1320

FPGA ARM based SOC module : TXZ-1320FPGA ARM based SOC module : TXZ-1320

/* 聯豪科創 統一產品頁面視覺框架 */

.tp-product-page { color: #333; font-family: "Segoe UI", "Roboto", "PingFang TC", sans-serif; line-height: 1.7; }

.tp-main-color { color: #0d1735; }

.tp-section { padding: 60px 20px; max-width: 1200px; margin: 0 auto; }

/* Hero Header - 採樣專家深藍漸層 */

.tp-product-hero { background: linear-gradient(135deg, #0d1735 0%, #000 100%); color: #fff; padding: 80px 20px; text-align: center; border-radius: 0 0 50px 50px; }

.tp-product-hero h1 { font-size: 38px; margin-bottom: 15px; font-weight: 800; letter-spacing: 1px; }

.tp-product-hero p { font-size: 18px; opacity: 0.9; max-width: 900px; margin: 0 auto; font-style: italic; }

/* Feature Grid - 三欄式佈局 */

.tp-feature-grid { display: grid; grid-template-columns: repeat(3, 1fr); gap: 30px; margin: 40px 0; }

.tp-feature-item { text-align: center; padding: 30px; background: #fdfdfd; border: 1px solid #eee; border-radius: 12px; transition: 0.3s; height: 100%; box-sizing: border-box; }

.tp-feature-item:hover { box-shadow: 0 10px 30px rgba(0,0,0,0.08); transform: translateY(-5px); }

.tp-feature-item i { font-size: 40px; color: #0d1735; margin-bottom: 15px; display: block; }

.tp-feature-item h3 { font-size: 18px; color: #0d1735; margin-bottom: 12px; font-weight: 700; }

/* Tech Highlights Section */

.tp-highlight-content { background: #f4f7fa; padding: 40px; border-radius: 20px; margin-bottom: 50px; }

.tp-list { list-style: none; padding: 0; }

.tp-list li { position: relative; padding-left: 30px; margin-bottom: 15px; font-size: 16px; }

.tp-list li::before { content: "✔"; position: absolute; left: 0; color: #0d1735; font-weight: bold; }

/* Spec Table Style */

.tp-spec-container { overflow-x: auto; margin-top: 40px; }

.tp-spec-table { width: 100%; border-collapse: collapse; background: #fff; min-width: 600px; }

.tp-spec-table th { background: #0d1735; color: #fff; padding: 15px; text-align: left; font-size: 18px; }

.tp-spec-table td { padding: 12px 15px; border-bottom: 1px solid #eee; font-size: 15px; }

.tp-spec-table tr:nth-child(even) { background: #fafafa; }

.tp-spec-label { font-weight: 600; color: #0d1735; width: 35%; }

/* CTA Section */

.tp-cta-box { background: #0d1735; color: #fff; padding: 50px; text-align: center; border-radius: 20px; margin-top: 60px; }

.tp-cta-btn { display: inline-block; background: #fff; color: #0d1735 !important; padding: 15px 40px; border-radius: 50px; text-decoration: none; font-weight: 700; margin-top: 25px; transition: 0.3s; }

.tp-cta-btn:hover { background: #000; color: #fff !important; transform: scale(1.05); }

/* RWD */

@media (max-width: 992px) { .tp-feature-grid { grid-template-columns: repeat(2, 1fr); } }

@media (max-width: 600px) { .tp-feature-grid { grid-template-columns: 1fr; } .tp-product-hero h1 { font-size: 28px; } }

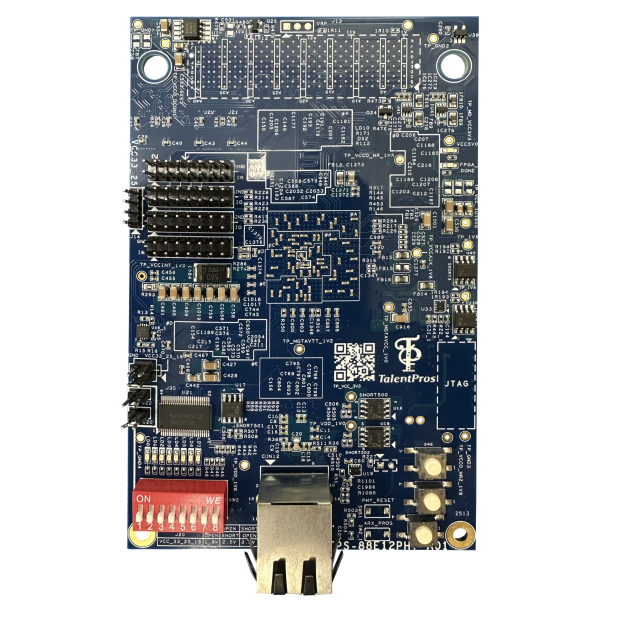

TPS-Z7020 Multi-Function Board

Advanced Acquisition & Logic Control: Precision Sensing Meets Heterogeneous Computing.

整合 16 通道數位化器與 LVDS 模式接收器,為晶片掃描測試與高速工業控制提供全方位的異構解決方案。

16-CH High-Speed Digitizer

內建 16 通道數位化器與靈活的 DIO 控制器,實現多點並行的高精度信號採集與處理。

Algorithm Accelerator

利用 Zynq-7020 的 85K 邏輯單元實現硬體加速,大幅提升實時信號分析與運算效能。

LVDS Pattern Receiver

板載 LVDS / mini LVDS 測試模式接收器,專為顯示介面驗證與高速序列數據接收設計。

定義高密度的數據採集與邊緣控制

TPS-Z7020 是一款專為複雜測試環境設計的多功能控制平台。透過 Xilinx Zynq-7000 SoC 架構,它將 演算法加速器 (Algorithm Accelerator) 與 網路存取控制 (Network Access) 封裝在超小尺寸的 PCB 空間內,不僅優化了 高速訊號整合 (Signal Integrity),更為工業 4.0 應用提供了極速的 上市時程 (Time-to-market) 優勢。

多通道晶片掃描測試: 支援板載多通道 Chip Scan In/Out 測試,是半導體驗證與除錯的理想選擇。

強大的存取資源: 配備 1GB DDR3 大容量緩存與 4GB eMMC 存儲,滿足大數據量採集的緩衝需求。

彈性的 I/O 擴充: 提供多達 115 組 PL User I/O,支援各種自定義工業周邊介面對接。

完善的網路連接: 整合 Gigabit Ethernet 與 USB 2.0 PHY,實現高效的遠端監控與數據回傳。

Technical Specifications

TPS-Z7020 Hardware Resources

Core SoC

Xilinx Zynq-7020 (XC7Z020-CLG400) | 85K Logic Cells

Memory & Storage

1GB DDR3 RAM | 4GB eMMC Flash

Digitizer & I/O

16 Channels Digitizer + DIO | Digital I/O Controller

Signal Interface

LVDS / mini LVDS Pattern Receiver on Board

Test Capabilities

Multi-channel Chip Scan In/Out Support

Communications

Gigabit Ethernet PHY | USB 2.0 PHY

Functional Blocks

Algorithm Accelerator | Network Access Controller

User I/O Pins

115 PL Pins | 10 PS MIO Pins

Physical & Power

101 x 57 mm Small Form Factor | 5V~12V Power In

Request Full Technical Documentation

Detailed datasheets, API SDKs, and hardware setup guides for TPS-Z7020 are available upon request.

Please contact our technical team for more information regarding Data Acquisition & Control solutions.

Contact Our Technical Team -

MORE

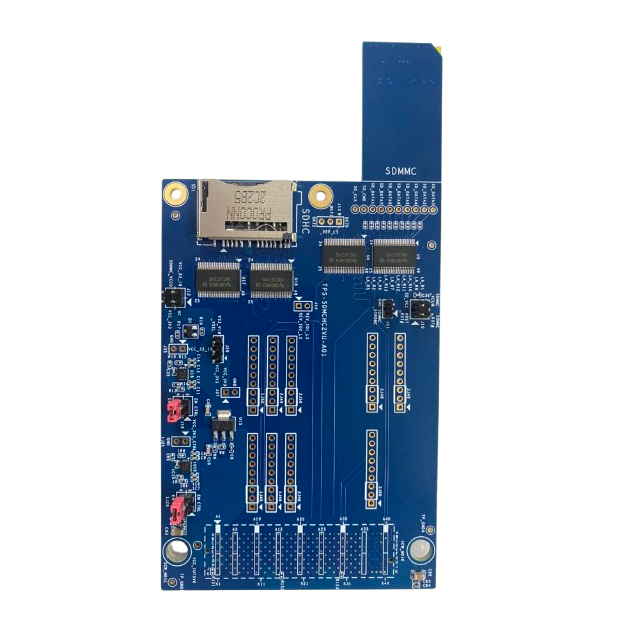

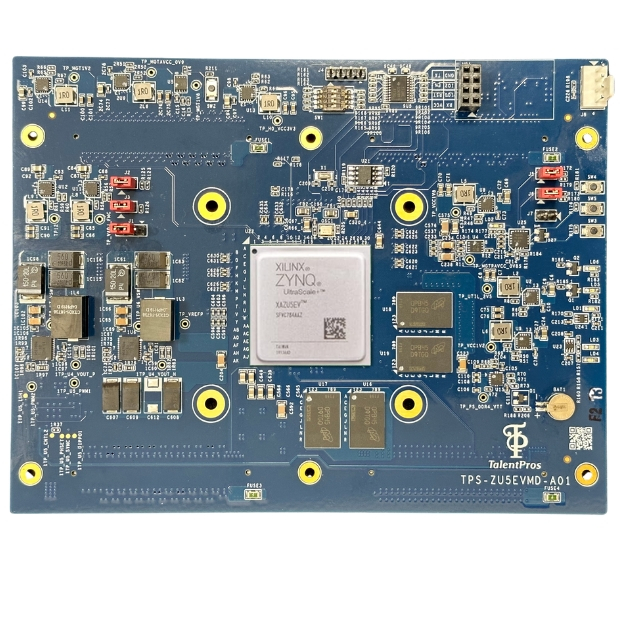

Xilinx Zynq UltraScale+ MPSOC _ TPS-ZU5EV / ZU7EV SoM

Xilinx Zynq UltraScale+ MPSOC _ TPS-ZU5EV / ZU7EV SoMXilinx Zynq UltraScale+ MPSOC _ TPS-ZU5EV / ZU7EV SoM

Zynq® UltraScale+™ MPSOC 5EV / 7EV

SPI flash memory (8 Mb)*1

DDR4 256 Mb x 16 SDRAMs component memory (4 Gb) *4

Size:116.8mm*152.4mm

Operating Voltage: 12VDC